65V/200mA

Sync. Step-Down Converter

Preliminary Specifications Subject to Change without Notice

## **DESCRIPTION**

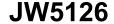

The JW®5126 is a monolithic buck switching regulators based on scheme of hysteresis mode. Operating with an input range of 4.5V~65V, JW5126 delivers 200mA of continuous output current with one integrated N-Channel MOSFET and one integrated P-Channel MOSFET. The internal synchronous power switches provide high efficiency without the use of an external Schottky diode. In order to achieve high efficiency at no load while maintaining output voltage regulation, JW5126 operates in low quiescent current and low frequency to maintain high efficiency.

JW5126 guarantees robustness with output short protection, thermal protection, current run-away protection and input under voltage lockout.

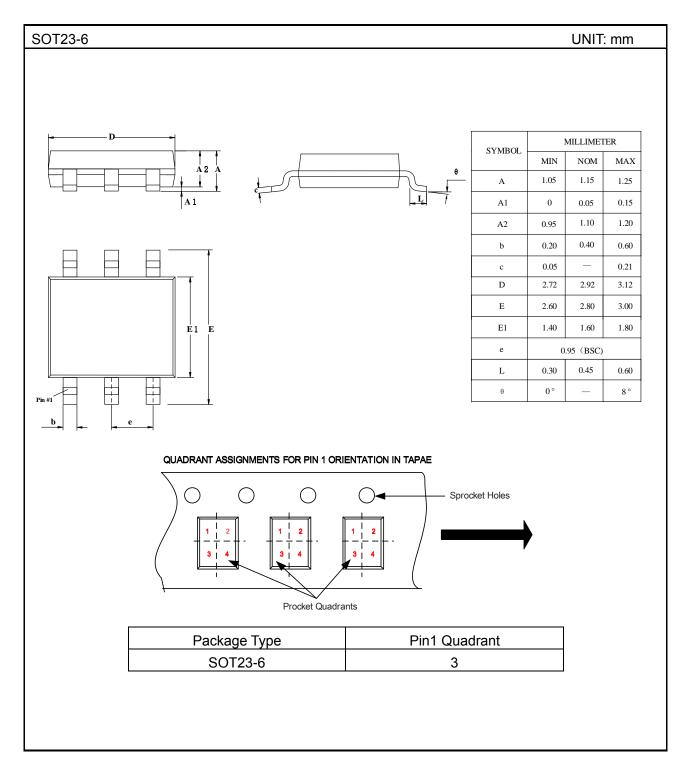

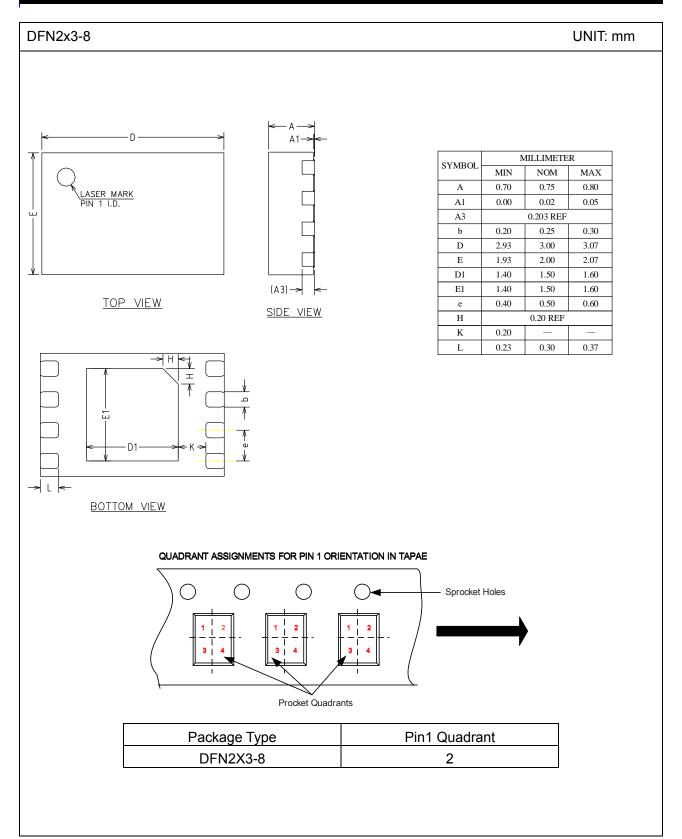

JW5126 is available in SOT23-6 and DFN2X3-8 package, which provide a compact solution with minimal external components.

Company's Logo is Protected, "JW" and "JOULWATT" are Registered Trademarks of JoulWatt technology Inc.

## **FEATURES**

- 4.5V to 65V operating input range 200mA output current

- Ultra high efficiency at light load

- Adjustable peak current limit

- Internal soft-start (SOT23-6)

- External Soft-start (DFN2X3-8)

- Power Good Indicator (DFN2X3-8)

- Adjustable UVLO and hysteresis

- Current run-away protection

- Output short protection

- Thermal protection

- Available in SOT23-6 and DFN2X3-8 packages

## **APPLICATIONS**

- MCU Supply in Wireless LED Lighting

- Wireless Charger

- Green Electronics/ Appliances

- Point of Load Regulation for High-Performance DSPs

- Industrial and Commercial Low Power Systems

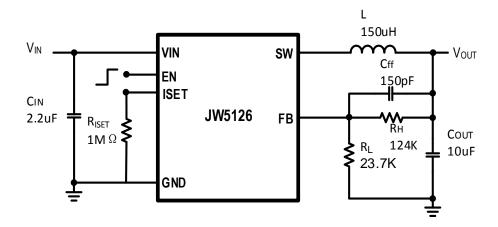

## TYPICAL APPLICATION

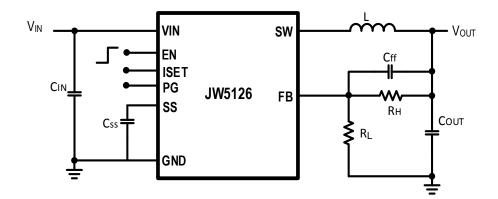

## ORDER INFORMATION

| DEVICE <sup>1)</sup> | PACKAGE  | TOP MARKING <sup>2)</sup> |

|----------------------|----------|---------------------------|

| JW5126DFNF#TRPBF     | DFN2X3-8 | JWGU□<br>YW□□□            |

| JW5126SOTB#TRPBF     | SOT23-6  | JWGT□<br>YW□□□            |

## Notes:

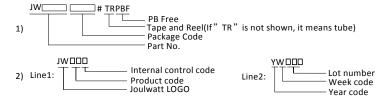

## **PIN CONFIGURATION**

## **TOP VIEW**

# **ABSOLUTE MAXIMUM RATING**1)

| VIN, SW Pin                        | 0.3V to 72V                             |

|------------------------------------|-----------------------------------------|

| SW Pin                             | 0.3V(-5V for 10ns) to 72V(74V for 20ns) |

| BST Pin                            | SW-0.3V to SW+5V                        |

| All other Pins                     | 0.3V to 6V                              |

| Junction Temperature <sup>2)</sup> | 150°C                                   |

| Lead Temperature                   | 260°C                                   |

| Storage Temperature                | -65°C to +150°C                         |

# **RECOMMENDED OPERATING CONDITIONS<sup>3)</sup>**

| Input Voltage VIN                 | 4                                 | .5V to 65V                      |  |

|-----------------------------------|-----------------------------------|---------------------------------|--|

| Junction Temperature Range        | 40°                               | C to 125°C                      |  |

| Ambient Temperature Range         | 40°C to 85°C                      |                                 |  |

| THERMAL PERFORMANCE <sup>4)</sup> | $	heta_{\scriptscriptstyle J\!A}$ | $	heta_{\scriptscriptstyle Jc}$ |  |

| DFN2X3-8                          | 62                                | 7.2°C/W                         |  |

| SOT23-6                           | 200                               | 130°C/W                         |  |

#### Note:

- 2) The JW5126 includes thermal protection that is intended to protect the device in overload conditions. Continuous operation over the specified absolute maximum operating junction temperature may damage the device.

- 3) The device is not guaranteed to function outside of its operating conditions.

- 4) Measured on JESD51-7, 4-layer PCB

<sup>1)</sup> Exceeding these ratings may damage the device. These stress ratings do not imply function operation of the device at any other conditions beyond those indicated under RECOMMENDED OPERATING CONDITIONS.

# **ELECTRICAL CHARACTERISTICS**

| VIN=12V, $T_A$ =25 $C_F$ Unless otherwise stated               |                       |                                                                                           |      |                           |      |      |

|----------------------------------------------------------------|-----------------------|-------------------------------------------------------------------------------------------|------|---------------------------|------|------|

| Item                                                           | Symbol                | Conditions                                                                                | Min. | Тур.                      | Max. | Unit |

| V <sub>IN</sub> Under Voltage Lock-out Threshold               | V <sub>IN_MIN</sub>   | V <sub>IN</sub> rising                                                                    | 4.0  | 4.2                       | 4.49 | V    |

| V <sub>IN</sub> Under voltage Lockout Hysteresis <sup>5)</sup> | VIN_MIN_HYST          |                                                                                           |      | 240                       |      | mV   |

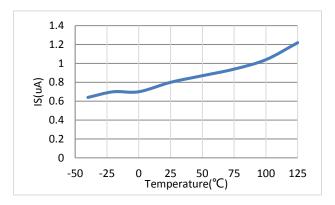

| Shutdown Supply Current                                        | I <sub>SD</sub>       | V <sub>EN</sub> =0V                                                                       |      |                           | 1    | μA   |

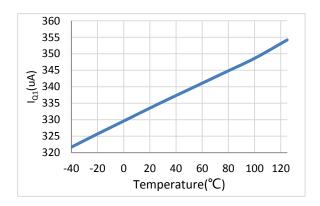

| Supply Current                                                 | I <sub>Q1</sub>       | Active Mode                                                                               |      | 330                       | 400  | μΑ   |

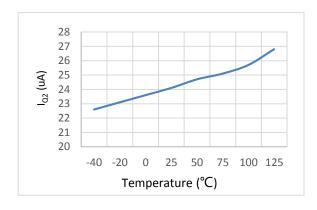

| Supply Current                                                 | I <sub>Q2</sub>       | Sleep Mode                                                                                |      | 26                        | 40   | μA   |

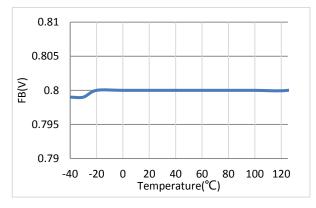

| Feedback Voltage                                               | V <sub>FB</sub>       |                                                                                           | 792  | 800                       | 808  | mV   |

| Feedback Pin Current                                           | lғв                   |                                                                                           | -100 | 0                         | 100  | nA   |

| Top Switch Resistance                                          | R <sub>DS(ON)T</sub>  |                                                                                           |      | 3.5                       |      | Ω    |

| Bottom Switch Resistance                                       | R <sub>DS(ON)B</sub>  |                                                                                           |      | 1.3                       |      | Ω    |

| Top Switch Leakage Current                                     | I <sub>LEAK_TOP</sub> | V <sub>IN</sub> =65V, V <sub>EN</sub> =0V,                                                |      |                           | 1    | μA   |

| Bottom Switch Leakage Current                                  | ILEAK_BOT             | V <sub>SW</sub> =0V<br>V <sub>IN</sub> =65V, V <sub>EN</sub> =0V,<br>V <sub>SW</sub> =65V |      |                           | 8    | μΑ   |

|                                                                |                       | $1M\Omega$ from ISET to GND                                                               |      | 340                       |      | mA   |

| Lliah Sida Dook Current Limit                                  | l                     | ISET Floating                                                                             | 200  | 340<br>235 270<br>140 170 | mA   |      |

| High-Side Peak Current Limit                                   | ILIMIT1               | 500k $\Omega$ from ISET to GND                                                            | 112  |                           | 170  | mA   |

|                                                                |                       | ISET short to GND                                                                         | 40   | 50                        | 60   | mA   |

| Peak Current Comparator Propagation  Delay Time <sup>5)</sup>  | T_delay               |                                                                                           |      | 48                        |      | ns   |

| Low-side Current Limit                                         | I <sub>LIMIT2</sub>   | $1M\Omega$ from ISET to GND                                                               |      | 134                       |      | mA   |

| Top Switch Minimum On Time <sup>5)</sup>                       | T <sub>ON_MIN</sub>   |                                                                                           |      | 115                       |      | ns   |

| EN Rising Threshold                                            | V <sub>EN_H</sub>     | V <sub>EN</sub> rising                                                                    | 1.1  | 1.2                       | 1.3  | V    |

| EN Falling Threshold                                           | V <sub>EN_L</sub>     | V <sub>EN</sub> falling                                                                   | 1.0  | 1.1                       | 1.2  | V    |

| EN Hysteresis                                                  | V <sub>EN_HYS</sub>   | V <sub>EN</sub> Hysteresis                                                                |      | 100                       |      | mV   |

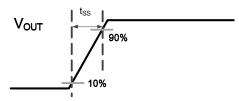

| Soft-Start Period <sup>5) 6)</sup>                             | t <sub>SS</sub>       | SS floating                                                                               |      | 0.65                      |      | ms   |

| Soft-Start Charging Current                                    | Iss                   | Vss = 1 V<br>@DFN2X3-8                                                                    |      | 2.5                       |      | uA   |

| Power Good Threshold - Rising                                  | PG_High               | VFB Rising<br>(% of FB voltage)<br>@DFN2X3-8                                              |      | 91                        |      | %    |

| Power Good Threshold - Falling                                 | PG_Low                | VFB Falling                                                                               |      | 87                        |      | %    |

4

| VIN=12V, $T_A$ =25 $\mathcal{C}$ , Unless otherwise stated |                       |                                |      |           |      |      |

|------------------------------------------------------------|-----------------------|--------------------------------|------|-----------|------|------|

| ltem                                                       | Symbol                | Conditions                     | Min. | Тур.      | Max. | Unit |

|                                                            |                       | (% of FB voltage)<br>@DFN2X3-8 |      |           |      |      |

| Power Cood Poley Time()                                    | DCD                   | Low to high @DFN2X3-8          |      | 340<br>13 | us   |      |

| Power Good Delay Time <sup>5)</sup>                        | PGD_ <sub>DLY</sub>   | High to low @DFN2X3-8          |      |           |      | us   |

| Power Good Sink Current                                    | lpg                   | PG=0.5V<br>@DFN2X3-8           | 3    |           |      | mA   |

| Thermal Shutdown <sup>5)</sup>                             | T <sub>TSD</sub>      |                                |      | 150       |      | °C   |

| Thermal Shutdown Hysteresis <sup>5)</sup>                  | T <sub>TSD_HYST</sub> |                                |      | 20        |      | °C   |

## Note:

- 5) Guaranteed by design.

- 6) Soft-Start Period is tested from 10% to 90% of the steady state output voltage.

tss Waveform

# **PIN DESCRIPTION**

| DFN2X3-8 | SOT23-6 | Name                                                                    | Description                                                                       |

|----------|---------|-------------------------------------------------------------------------|-----------------------------------------------------------------------------------|

| 1        | 1 3 EN  |                                                                         | Enable Control Input. Drive EN pin high or floating to turn on the regulator and  |

|          |         | LIN                                                                     | low to turn off the regulator.                                                    |

| 2        | 1       | FB                                                                      | Output feedback pin. Connect a resistive divider at FB.                           |

| 3        |         | PG                                                                      | Power good open drain output. Asserts low if output voltage is low due to         |

| 3        |         |                                                                         | OTP, UVP, UVLO, EN shutdown or during soft-start.                                 |

| 4        | 4 6 SW  | SW is the switching node that supplies power to the output. Connect the |                                                                                   |

| 4        |         | SVV                                                                     | output LC filter from SW to the output load.                                      |

| 5        | 2       | GND                                                                     | Power ground.                                                                     |

|          | 5       | 5 VIN                                                                   | Input voltage pin. VIN supplies power to the IC. Connect a 4.5V to 65V supply     |

| 6        |         |                                                                         | to VIN and bypass VIN to GND with a suitably large capacitor to eliminate         |

|          |         |                                                                         | noise on the input to the IC.                                                     |

| 7        | 7       |                                                                         | Soft-start control pin. Leave floating for internal soft-start slew rate. Connect |

| ,        |         | SS                                                                      | to a capacitor to extend soft start time.                                         |

|          |         |                                                                         | High-side peak current set pin. A resistor from this pin to GND sets the          |

|          |         |                                                                         | high-side peak current limit. Leave floating for 235mA. Connect 500kΩ             |

| 8        | 4       | ISET                                                                    | resistance for the maximum peak current 140mA. Short this pin to GND for          |

|          |         |                                                                         |                                                                                   |

|          |         |                                                                         | peak current 340mA and low side valley current 134mA.                             |

| Exposed  |         | GND                                                                     | GND pin must be electrically connected to the exposed pad on the printed          |

| Pad      |         | GIVD                                                                    | circuit board for proper operation.                                               |

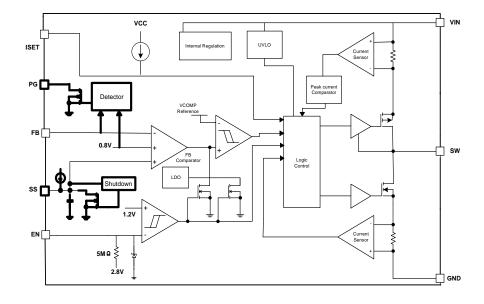

# **BLOCK DIAGRAM**

# TYPICAL PERFORMANCE CHARACTERISTICS

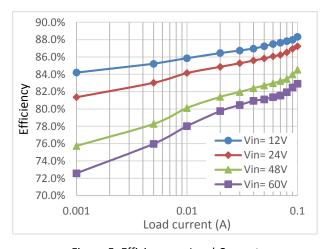

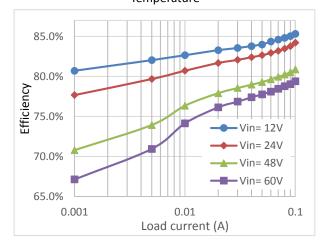

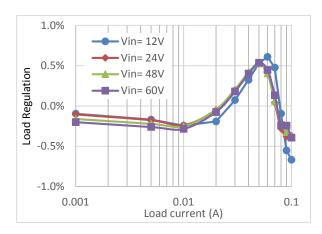

$V_{IN}$  =24V,  $V_{OUT}$ = 5V, L = 150 $\mu$ H,  $C_{OUT}$  = 10 $\mu$ F,ISEL=Floating,  $T_A$  = +25°C, unless otherwise noted

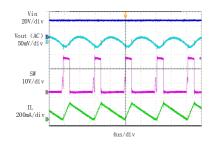

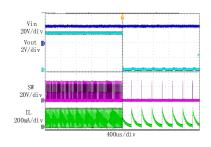

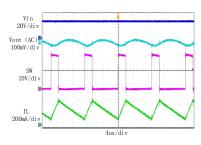

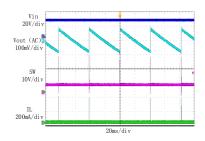

#### **Steady State Test**

$V_{IN}$ =24V,  $V_{OUT}$ =5V  $I_{OUT}$ =0.1A

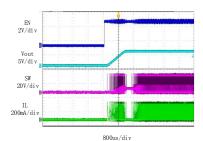

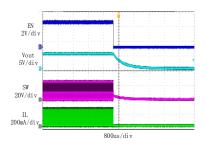

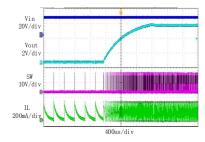

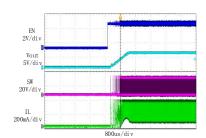

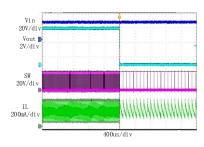

#### Startup through Enable

V<sub>IN</sub>=24V, V<sub>OUT</sub>=5V I<sub>OUT</sub>=0.1A (Resistive load)

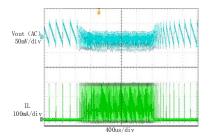

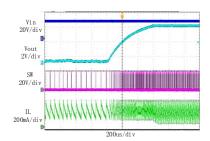

#### Shutdown through Enable

$V_{IN}$ =24V,  $V_{OUT}$ =5V  $I_{OUT}$ =0.1A (Resistive load)

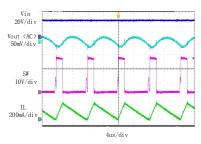

## **Heavy Load Operation**

0.1A LOAD

## **Light Load Operation**

0.05A LOAD

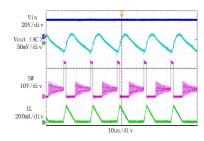

# No Load Operation

0 A LOAD

#### **Short Circuit Protection**

$V_{IN}$ =24V,  $V_{OUT}$ =5V  $I_{OUT}$ =0.1A- Short

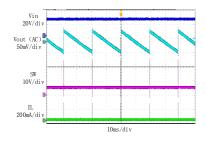

#### **Short Circuit Recovery**

$V_{IN}$ =24V,  $V_{OUT}$ =5V  $I_{OUT}$ = Short-0.1A

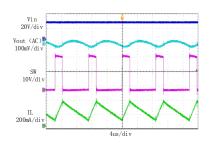

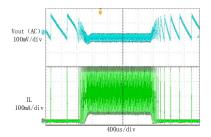

#### **Load Transient**

$0A LOAD \rightarrow 0.1A LOAD \rightarrow 0A LOAD$

Cff=150pF

## TYPICAL PERFORMANCE CHARACTERISTICS

$V_{IN}$  =24V,  $V_{OUT}$ = 5V, L = 150 $\mu$ H,  $C_{OUT}$  = 10 $\mu$ F,ISEL= 1M  $\Omega$  ,  $T_A$  = +25°C, unless otherwise noted

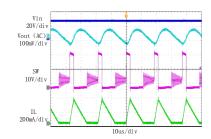

#### **Steady State Test**

$V_{IN}$ =24V,  $V_{OUT}$ =5V  $I_{OUT}$ =0.2A

#### Startup through Enable

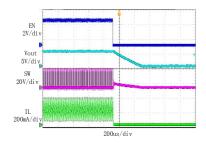

V<sub>IN</sub>=24V, V<sub>OUT</sub>=5V I<sub>OUT</sub>=0.2A (Resistive load)

#### Shutdown through Enable

$V_{IN}$ =24V,  $V_{OUT}$ =5V  $I_{OUT}$ =0.2A (Resistive load)

## **Heavy Load Operation**

0.2A LOAD

## **Light Load Operation**

0.1A LOAD

## No Load Operation

0 A LOAD

#### **Short Circuit Protection**

$V_{IN}$ =24V,  $V_{OUT}$ =5V  $I_{OUT}$ =0.2A- Short

#### **Short Circuit Recovery**

$V_{IN}$ =24V,  $V_{OUT}$ =5V  $I_{OUT}$ = Short-0.2A

#### **Load Transient**

$0 \text{A LOAD} \rightarrow 0.2 \text{A LOAD} \rightarrow 0 \text{A LOAD}$

Cff=150pF

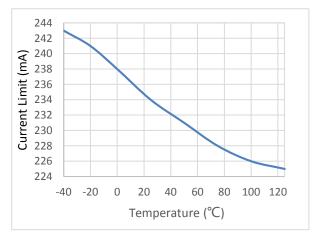

## TYPICAL PERFORMANCE CHARACTERISTICS

Figure 1. Iq1 vs Junction Temperature

Figure 2. IQ2 vs Junction Temperature

Figure 3. Shutdown Current vs Junction Temperature

Figure 4. FB Voltage Regulaion vs Junction

Temperature

Figure 5. Efficiency vs Load Current  $(V_{OUT}=5V, L=150\mu H)$

Figure 6. Efficiency vs Load Current ( $V_{OUT} = 3.3V$ , L=150 $\mu$ H)

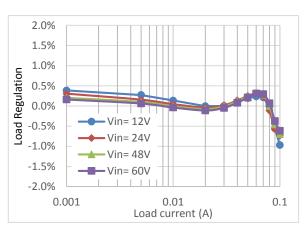

## TYPICAL PERFORMANCE CHARACTERISTICS

Figure 7. Load Regulation vs Load Current

$(V_{OUT} = 5V, L = 150 \mu H)$

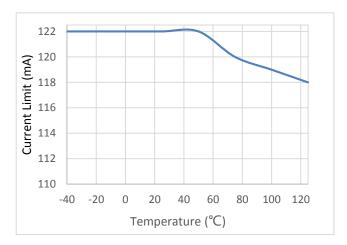

Figure 9. High-Side Peak Current Limit vs Junction Temperature@ Rlimit=Floating

Figure 8. Load Regulation vs Load Current

$(V_{OUT} = 3.3V, L = 150 \mu H)$

Figure 10. Low-Side Current Limit vs Junction Temperature @Rlimit=1MHz

## **FUNCTIONAL DESCRIPTION**

JW5126 is a synchronous step-down regulator based on scheme of hysteresis mode. It regulates input voltages from 4.5V to 65V down to an output voltage as low as 0.8V, and is capable of supplying up to 200mA of load current.

## **Scheme of Hysteresis Mode**

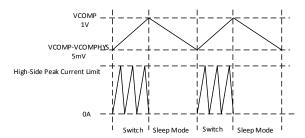

After comparing the FB voltage with the internal reference voltage 0.8V, the voltage VCOMP can be obtained by integrating the error amplifier. Comparing VCOMP to an internal 1V reference, as shown in Figure11. If this voltage is greater than the reference, the comparator activates a sleep mode in which the power switches and current comparators are disabled, reducing the VIN pin supply current to only  $26\mu A$ . As the load current discharges the output capacitor, the VCOMP decreases. When this voltage falls 5mV below the 1V reference, the feedback comparator trips. The internal high-side power switch (P-channel MOSFET) is turned on and the inductor current begins to ramp up.

The inductor current increases until either the current exceeds the peak current comparator threshold, or the ON time of the high-side MOSFET exceeds 5µs during the time VCOMP is higher than 1V, at which the high-side power switch is turned off, and the Low-side power switch is turned on.

When  $0\,\Omega$  <=R<sub>ISET</sub><=649K  $\Omega$  or R<sub>ISET</sub> =floating, the inductor current ramps down until the reverse current is close to zero. If the VCOMP is still less than the 1V reference, the high-side power switch is turned on again and another cycle commences which keep the inductor current operated in a boundary conduction mode. The average current during the BCM will

normally be greater than the average load current. For this architecture, the maximum average output current is equal to half of the peak current. The hysteresis nature of this control architecture results in a switching frequency that is a function of the input voltage, output voltage and inductor value.

Figure 11. Scheme of Hysteresis Mode

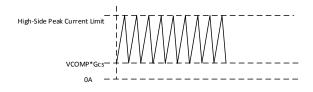

When a  $1M\Omega$  (820K~1.2M) from ISET to GND, the JW5126 operating in CCM at  $I_{OUT}$  larger than 1/2\*ILIMIT1, as shown in Figure12. The inductor current increases until either the current exceeds the peak current comparator threshold, or the ON time of the high-side MOSFET exceeds 5µs during the time VCOMP is higher than 1V, at which the high-side power switch is turned off, and the Low-side power switch is turned on. The inductor current ramps down until the inductance current is lower than  $V_{COMP}$ -Gcs. Then the high-side switch is turned on.

Figure 12. CCM Mode

#### **Shut-Down Mode**

The regulator shuts down when voltage at EN pin is driven below 0.3V. The entire regulator is

off and the supply current consumed by the regulator drops below  $1\mu A$ .

# Enable and Adjustable UVLO Protection

The JW5126 is enabled when the VIN pin voltage rises above 4.2V and the EN pin voltage exceeds the enable threshold of 1.2V. The JW5126 is disabled when the VIN pin voltage falls below 3.9V or when the EN pin voltage is below 1.1V. The EN pin has an internal pull-up resistor that enables operation of the JW5126 when the EN pin floats.

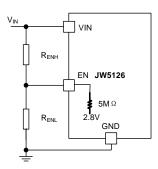

If an application requires a higher VIN under-voltage lockout (UVLO) threshold, use a resistive divider connected between VIN and ground with the central tap connected to EN to adjust the input voltage UVLO. (Shown in Figure 13). So that when VIN rises to the pre-set value, EN rises above 1.2V to enable the device and when  $V_{\rm IN}$  drops below the pre-set value, EN drops below 1.1V to trigger input under voltage lockout protection.

Figure 13. Adjustable UVLO

The input voltage UVLO threshold ( $V_{UVLO}$ ) and hysteresis ( $V_{UVLO\_HYS}$ ) can be calculated by the following equation.

$$\begin{split} V_{UVLO} = & \left(V_{EN\_H} - \frac{2.8V}{5M\Omega * \frac{R_{ENH} + R_{ENL}}{R_{ENH} * R_{ENL}} + 1}\right) \\ & * \left(R_{ENH} * \frac{5M\Omega + R_{ENL}}{5M\Omega * R_{ENL}} + 1\right) \end{split}$$

$$V_{UVLO\_HYS} = \left(R_{ENH} * \frac{5M\Omega + R_{ENL}}{5M\Omega * R_{ENL}} + 1\right) * V_{EN\_HYS}$$

When R<sub>ENL</sub> <=100K  $\Omega$  ,  $V_{UVLO}$  can be calculated approximately according to the following equation.

$$\begin{split} V_{UVLO} &= \frac{R_{ENH} + R_{ENL}}{R_{UVLO\_lower}} * V_{EN\_H} \\ V_{UVLO\_HYS} &= \frac{R_{ENH} + R_{ENL}}{R_{ENL}} * V_{EN\_HYS} \end{split}$$

where

$V_{EN\_H}$  is enable shutdown threshold (1.2V typ.);  $V_{EN\_HYS}$  is enable shutdown hysteresis (100mV typ.);

## **Output Short Protection**

JW5126 inherent short–circuit protection. If the output is shorted to ground, the inductor current will decay very slowly during a single switching cycle. Since the high-side switch turns on only when the inductor current is near zero at 0  $\Omega$  <=R\_ISET<=649K  $\Omega$  or R\_ISET =floating, or near 134mA at R\_ISET =1M $\Omega$  (820K~1.2M), the JW5126 inherently switches at a lower frequency during short-circuit condition.

#### **External Soft-start**

#### (DFN2X3-8)

Soft-start is designed in DFN2X3-8 package to prevent the converter output voltage from overshooting during startup and short-circuit recovery. An internal current source ( $I_{SS}$ ) of 2.5uA is designed to charge the external soft-start capacitor ( $C_{SS}$ ). When it is less than internal reference voltage ( $V_{REF}$ , typ. 0.8V), SS voltage overrides  $V_{REF}$  and the error amplifier uses SS voltage as the reference. When SS exceeds  $V_{REF}$ ,  $V_{REF}$  regains control.

The soft start time  $T_{\text{SS}}$  can be calculated by the following equation.

$$T_{SS}(ms) = \frac{0.8 * C_{SS}(nF) * V_{REF}(V)}{I_{SS}(uA)}$$

#### **Power Good**

## (DFN2X3-8)

The DFN2X3-8 package has power-good (PG) output. The PG pin is the open drain of a MOSFET. Connect to a voltage source (such as  $V_{OUT}$ ) through a resistor. When the FB voltage exceeds 91% of the internal reference  $V_{REF}$ , the internal PG switch turns off and PG can be pulled high by the external pull-up. If the FB voltage falls below 87% of  $V_{REF}$ , the internal PG

switch turns on, and PG is pulled low to indicate that the output voltage is out of regulation. The rising edge of PG has a built-in deglitch delay of  $340~\mu s$ .

#### Thermal Protection

When the temperature of the regulator rises above 150°C, it is forced into thermal shut-down. Only when core temperature drops below 130°C can the regulator becomes active again.

## APPLICATION INFORMATION

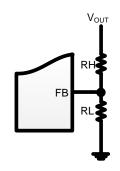

## **Output Voltage Set**

The output voltage is determined by the resistor divider connected at the FB pin, and the voltage ratio is:

$$V_{FB} = V_{OUT} * \frac{R_L}{R_H + R_L}$$

where  $V_{\text{FB}}$  is the feedback voltage and  $V_{\text{OUT}}$  is the output voltage.

If  $R_L$  is determined, and then  $R_H$  can be calculated by:

$$R_{\rm H} = R_{\rm L} * \left(\frac{V_{\rm OUT}}{0.8} - 1\right)$$

# **High-Side Peak Current Limit**

The peak current can be programmed from 50mA to 236mA by changing the resistor between ISET pin and ground. The peak current setting resistor RISET can be calculated by the formula:

When

$$0 \Omega <= R_{ISET} <= 649 K \Omega$$

$$I_{LIMIT1}$$

(mA) = 0.18 \*  $R_{ISET}$  (K $\Omega$ ) + 50

When R<sub>ISET</sub> =floating

$$I_{LIMIT1}(mA) = 225mA$$

When 820K  $\Omega$  <=R<sub>ISET</sub><=1200K  $\Omega$

$I_{LIMIT1}~(mA)~=0.167*R_{ISET}~(K\Omega)~+193~$  When  $0\Omega <=R_{ISET} <=649 K\Omega~ or~R_{ISET}~=floating~$  setting  $I_{LIMT1},~be~ noticed~ that~ the~ maximum~$  output current is equal to half of the  $I_{LIMT1}.~Make~$  sure~ the  $I_{LIMT1}$  is high enough for the output current requirement. Also be noticed that higher

I<sub>LIMT1</sub> would result in higher inductor current ripple, larger input and output voltage ripple, which means bigger components (inductor, input and output capacitors).

When  $820 \text{K}\Omega <= R_{\text{ISET}} <= 1200 \text{K}\Omega$ , the maximum output current is equal to  $1/2^*(\ l_{\text{LIMT1}} +\ l_{\text{LIMT2}})$ , where  $l_{\text{LIMT2}}$  is low side current limit  $(I_{\text{LIMT2}} = 134 \text{mA})$ .

## **Output Capacitor**

The output capacitor,  $C_{\text{OUT}}$ , filters the inductor's ripple current and stores energy to satisfy the load current. when the JW5126 is in sleep mode. The value of the output capacitor must be large enough to accept the energy stored in the inductor without a large change in output voltage. To achieve an output voltage peak-peak ripple less than 1% of the output voltage, the output capacitor must be:

$$C_{OUT} \ge 50 * L * \left(\frac{I_{LIMIT1}}{V_{OUT}}\right)^2 * \frac{V_{IN}}{V_{IN} - V_{OUT}}$$

#### Inductor

As the  $I_{LIMT1}$  is determined, for given input voltage and output voltage, the inductor value can be determined by the following formula:

$$L = \frac{V_{OUT}}{f_{SW} * I_{LIMIT1}} * \left(1 - \frac{V_{OUT}}{V_{IN}}\right)$$

where  $V_{\rm IN}$  is the input voltage,  $V_{\rm OUT}$  is the output voltage,  $f_{\rm sw}$  is the switching frequency at the maximal output current, and  $I_{LIMIT1}$  is the high side peak current.

Larger inductor value results in lower switching frequency, as well as higher efficiency. However, the larger value inductor will have a larger physical size, higher series resistance, and lower saturation current as well as the slow load

transient dynamic performance. There is also a lower limit of the inductor value, which is determined by the minimum on time. In order to keep the inductor working under control, the inductor value should be chosen higher than L<sub>MIN</sub> that is derived from below formula:

$$L_{MIN} = \frac{V_{IN\_MAX} * T_{ON\_MIN}}{I_{LIMIT1}}$$

Where VIN\_MAX is the max value of input voltage. TON\_MIN is the designed 110ns minimum switch on time.

## **Switch Frequency**

Switching frequency can be estimated by below equation.

$$f_{sw} = \frac{2*I_{OUT}*V_{OUT}*(V_{IN} - V_{OUT})}{{I_{LIMIT1}}^2*V_{IN}*L}$$

Higher  $I_{\text{LIMIT1}}$  and inductor can get lower fsw. And fsw increases as  $I_{\text{OUT}}$  increasing. When  $I_{\text{OUT}}$  increases to  $I_{\text{LIMIT1}}/2$ , fsw also reaches its highest value and can be derived by:

$$f_{SW\_MAX} = \frac{V_{OUT} * (V_{IN} - V_{OUT})}{I_{LIMIT1} * V_{IN} * L}$$

## **PCB Layout Note**

For minimum noise problem and best operating performance, the PCB is preferred to following the guidelines as reference.

- Place the input decoupling capacitor as close to JW5126 (VIN pin and GND pin) as possible to eliminate noise at the input pin. The loop area formed by input capacitor and GND must be minimized.

- 2. Put the feedback trace as short as possible, and far away from the inductor and noisy power traces like SW node.

- 3. Keep the switching node SW short to prevent excessive capacitive coupling

- Make V<sub>IN</sub>, V<sub>OUT</sub> and ground bus connections as wide as possible. This reduces any voltage drops on the input or output paths of the converter and maximizes efficiency.

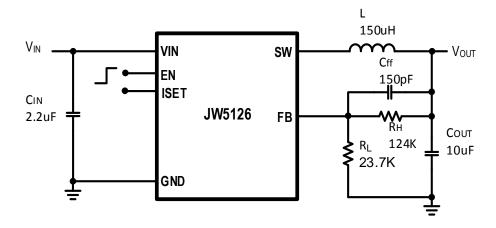

## **REFERENCE DESIGN For SOT23-6**

## Reference 1:

V<sub>IN</sub>: 6V~60V

V<sub>OUT</sub>: 5V

I<sub>OUT</sub>: 0~0.1A

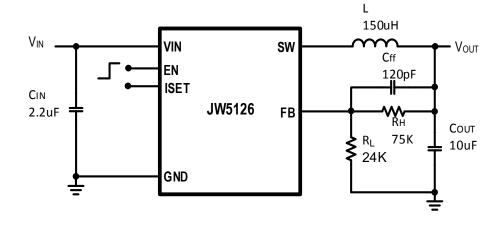

## Reference 2:

V<sub>IN</sub>: 4.5V~60V

V<sub>OUT</sub>: 3.3V

I<sub>OUT</sub>: 0~0.1A

## Reference 3:

V<sub>IN</sub>: 6V~60V

Vout: 5V

I<sub>OUT</sub>: 0~0.2A

## **PACKAGE OUTLINE**

JW5126 Rev.0.12

2021/05/17

## **IMPORTANT NOTICE**

Joulwatt Technology Inc. reserves the right to make modifications, enhancements, improvements, corrections or other changes without further notice to this document and any product described herein.

- Any unauthorized redistribution or copy of this document for any purpose is strictly forbidden.

- Joulwatt Technology Inc. does not warrant or accept any liability whatsoever in respect of any products purchased through unauthorized sales channel.

Copyright © 2020 JW5126 Incorporated.

All rights are reserved by Joulwatt Technology Inc.