# **JW1532B**

# High Efficiency Off-line CV Regulator

#### **DESCRIPTION**

The JW1532B is a high efficiency low cost off-line constant voltage regulator for Buck and Buck-Boost topology with 650V MOSFET.

JW1532B can output 18V/12V default voltage with few external components, which decreases the system cost. In light load condition, JW1532B operates in green mode, in which the inductor peak current and the switching frequency is lower than that of full load to improve the system efficiency and the reference voltage is decreased to ensure good load regulation.

JW1532B has multi-protection functions which largely enhance the safety and reliability of the system, including VDD under-voltage lockout (UVLO), short circuit protection (SCP), pulse-by-pulse current limit, over load protection (OLP) and over-temperature protection (OTP).

Company's Logo is Protected, "JW" and "JOULWATT" are Registered Trademarks of JoulWatt technology Co., Ltd.

### **FEATURES**

- Ultra Low System BOM Cost

- Integrated with 650V, Low R<sub>dson</sub> MOSFET

- 18V/12V Default Output Voltage

- Support Buck and Buck-Boost Topology

- Peak Current Mode Control

- Frequency Jittering for Good EMC

- High Efficiency Over Wide Operating Range

- Output Voltage Load Regulation Compensation

- VDD UVLO

- Short Circuit Protection

- Pulse-by-pulse Current Limit

- Over Temperature Protection

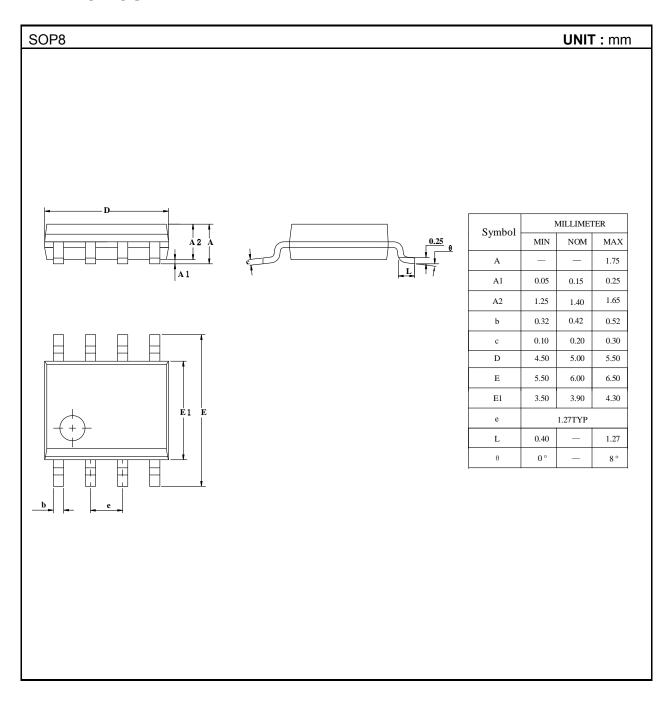

- SOP8 Package

#### **APPLICATIONS**

- Home Appliance

- Standby Power

- Consumer Electronics

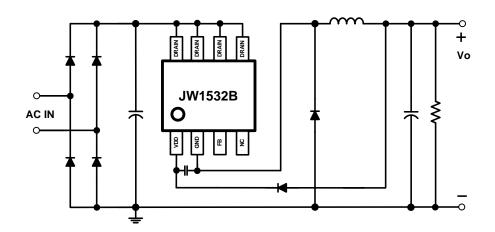

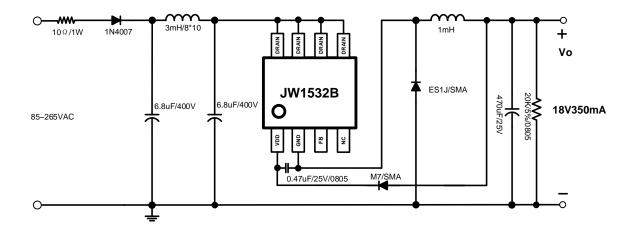

## TYPICAL APPLICATION

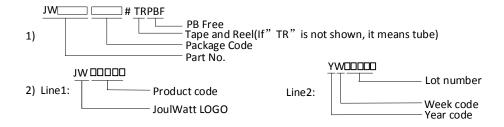

## **ORDER INFORMATION**

| DEVICE <sup>1)</sup>           | PACKAGE | TOP MARKING <sup>2)</sup> |  |

|--------------------------------|---------|---------------------------|--|

| 1/4/4 E 2 2 D C O D #T D D D E | CODS    | JW1532B                   |  |

| JW1532BSOPB#TRPBF              | SOP8    | YW□□□□                    |  |

#### Notes:

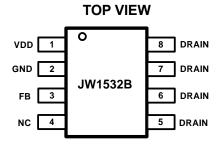

## **PIN CONFIGURATION**

# **ABSOLUTE MAXIMUM RATING**<sup>1)</sup>

| VDD Voltage to GND                    | 0.3V to 22V, 22V to 28V<1s |

|---------------------------------------|----------------------------|

| DRAIN Voltage to GND                  | 0.3V to 650V               |

| FB Voltage to GND                     | 0.3V to 6.5V               |

| Junction Temperature <sup>2) 3)</sup> | 150°C                      |

| Lead Temperature                      | 260°C                      |

| Storage Temperature                   | 65°C to +150°C             |

| ESD Susceptibility (Human Body Model) | 2.5kV                      |

## RECOMMENDED OPERATING CONDITIONS

| DRAIN Voltage to GND                               | 600V         |

|----------------------------------------------------|--------------|

| Operating Junction Temperature (T <sub>J</sub> )40 | 0°C to 125°C |

|         | Recommended MAX Output                |

|---------|---------------------------------------|

| Package | Current                               |

|         | (T <sub>J</sub> =125°C) <sup>4)</sup> |

| SOP8    | 450mA                                 |

| THERMAL PERFORMANCE <sup>5)</sup> | $	heta_{J\!A}$ | $	heta_{\!\scriptscriptstyle JC}$ |

|-----------------------------------|----------------|-----------------------------------|

| SOP8                              | 9645           | 5°C/W                             |

#### Note:

- 1) Exceeding these ratings may damage the device. These stress ratings do not imply function operation of the device at any other conditions beyond those indicated under RECOMMENDE OPERATING CONDITIONS.

- 2) The JW1532B includes thermal protection that is intended to protect the device in overload conditions. Continuous operation over the specified absolute maximum operating junction temperature may damage the device.

- **3)** The device is not guaranteed to function outside of its operating conditions.

- 4) The maximum output current is recommended in the application according to chip junction temperature T<sub>J</sub>=125°C (chip case temperature difference about 20°C). The maximum output current could be increased properly if the heat dissipation is better.

- 5) Measured on JESD51-7, 4-layer PCB.

# **ELECTRICAL CHARACTERISTICS**

| $T_{A}$ =25 °C, unless otherwise stated.        |                      |                        |        |      |        |              |

|-------------------------------------------------|----------------------|------------------------|--------|------|--------|--------------|

| Item                                            | Symbol               | Condition              | Min.   | Тур. | Max.   | Units        |

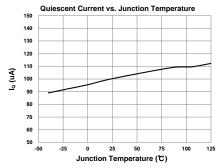

| VDD Quiescent Current                           | lα                   | V <sub>DD_ST</sub> -1V | 75     | 100  | 125    | μΑ           |

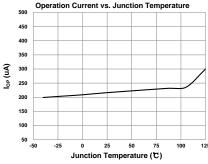

| Operation Current                               | I <sub>OP</sub>      | V <sub>DD_ST</sub> +1V | 200    | 215  | 230    | uA           |

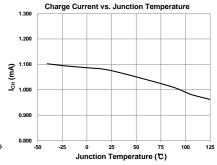

| VDD Charge Current                              | Існ                  | VDD=5V                 | 0.9    | 1    | 1.2    | mA           |

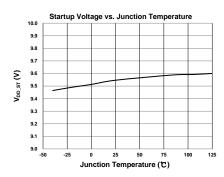

| VDD Startup Voltage                             | V <sub>DD_ST</sub>   |                        | 9.0    | 9.5  | 10.0   | V            |

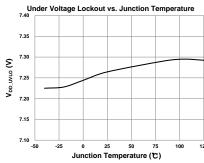

| VDD Under Voltage Lockout                       | V <sub>DD_UVLO</sub> |                        | 7.0    | 7.2  | 7.5    | V            |

| VDD Clamping Voltage                            | $V_{CLP}$            | Sink current =5mA      | 23     | 24   | 25     | V            |

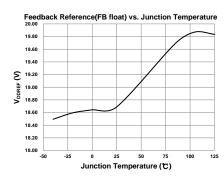

|                                                 | VDDREF               | FB floating            | 18.042 | 18.6 | 19.158 | V            |

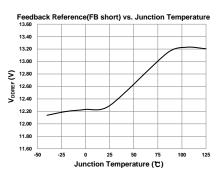

| VDD Feedback Reference                          |                      | FB short to GND        | 12.028 | 12.4 | 12.772 | V            |

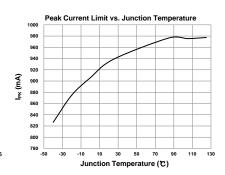

| Peak Current Limit                              | I <sub>PK</sub>      |                        | 0.79   | 0.9  | 1.09   | Α            |

| Oscillator Frequency                            | f <sub>osc</sub>     |                        | 60     | 70   | 78     | kHz          |

| Frequency Jittering Range                       | ±∆f/f <sub>OSC</sub> |                        |        | 8    |        | %            |

| Frequency Jittering Period                      | T <sub>Jit</sub>     |                        |        | 15   |        | ms           |

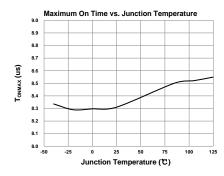

| Maximum On Time                                 | T <sub>ONMAX</sub>   |                        | 7.5    | 8.5  | 9.5    | μs           |

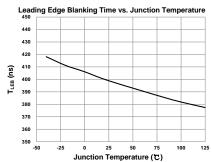

| Leading Edge Blanking Time                      | T <sub>LEB</sub>     |                        |        | 400  |        | ns           |

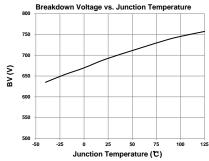

| MOS Breakdown Voltage                           | BV                   |                        | 650    | 690  |        | V            |

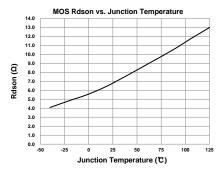

| MOS Rdson                                       | Rdson                | Vgs=10V                |        | 6    | 8      | Ω            |

| Over Thermal Protection Threshold <sup>6)</sup> |                      |                        |        | 150  |        | $^{\circ}$   |

| Over Thermal Protection Recovery  Hysteresis 6) |                      |                        |        | 30   |        | $^{\circ}$ C |

## Note:

6) Guaranteed by design.

## TYPICAL CHARACTERISTICS

## **PIN DESCRIPTION**

| Pin<br>SOP8 | Name  | Description                                                |

|-------------|-------|------------------------------------------------------------|

| 1           | VDD   | IC power supply and output voltage feedback                |

| 2           | GND   | IC ground                                                  |

| 3           | FB    | Output voltage setup, FB floating-18V, FB short to GND-12V |

| 4           | NC    |                                                            |

| 5           | DRAIN | Internal MOS drain and HV power supply                     |

| 6           | DRAIN | Internal MOS drain and HV power supply                     |

| 7           | DRAIN | Internal MOS drain and HV power supply                     |

| 8           | DRAIN | Internal MOS drain and HV power supply                     |

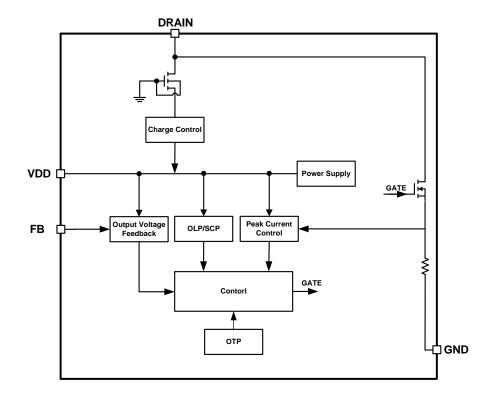

## **BLOCK DIAGRAM**

## **FUNCTIONAL DESCRIPTION**

JW1532B is a high efficiency low cost off-line constant voltage regulator for Buck and Buck-Boost topology.

## Start Up

JW1532B can be supplied from MOS DRAIN directly. When the internal high voltage(HV) power souse charges VDD up to the  $V_{DD\_ST}$ , the gate driver starts to switch. VDD will be powered by output voltage in steady state. Once the voltage of VDD is lower than  $V_{DD\_UVLO}$ , JW1532B stops switching.

#### **Peak Current Control**

JW1532B has the default peak current for output current. And it also has the SCP limit peak current for abnormal state such as inductance short.

## **Constant Voltage Control**

The output voltage is sensed by VDD pin and adjusted by internal control compensation loop automatically.

The switching frequency of JW1532B is fixed to  $f_{\rm osc}$  with  $\pm$  8% jittering to improve the EMI performance.

Output voltage can be selected by FB pin setup. If FB is floating, output voltage is 18V, if the FB pin is short to GND, output voltage is 12V.

#### **Green Mode**

In light or no load condition, JW1532B operates

in DCM which means the OFF time is very long. JW1532B will reduce the peak current of the inductor to minimize the power loss. The longer Toff, the lower  $I_{PK}$ .

# Short Circuit Protection (SCP)/ Over Load Protection (OLP)

In short circuit or over load condition, VDD can't be charged to  $V_{REF}$ . JW1532B will operate in auto-restart mode which is represented in the following description if VDD< $V_{REF}$  for some time.

#### **Auto-restart Mode**

JW1532B will enter auto-restart mode if SCP/OLP/OTP is triggered. The chip stops switching and the HV power source is disconnected until VDD decreases to  $V_{DD\_UVLO}$ . If VDD is charged to  $V_{DD\_ST}$  for several cycles, the system restarts.

### **Over Temperature Protection**

When internal temperature of the chip exceeds 150°C, JW1532B operates in auto-restart mode to help the chip cooling.

#### **PCB** Design

- 1. The VDD pin must be locally bypassed with a capacitor.

- 2. Make the area of the power loop as small as possible in order to reduce the EMI radiation.

## **APPLICATION REFERENCE**

Note: Information in the following reference design sections is not part of JoulWatt component specification. Customers are responsible for determining suitability of components chosen for their purposes and should validate their design implementation to make sure the proper system functionality.

The reference design is suitable for non-isolated buck power supply default 18V output, using JW1532B.

V<sub>IN</sub>: 85~265VAC

V<sub>OUT</sub>: 18V I<sub>OUT</sub>: 350mA

## **PACKAGE OUTLINE**

#### IMPORTANT NOTICE

Joulwatt Technology Co.,Ltd reserves the right to make modifications, enhancements, improvements, corrections or other changes without further notice to this document and any product described herein.

- Any unauthorized redistribution or copy of this document for any purpose is strictly forbidden.

- Joulwatt Technology Co.,Ltd does not warrant or accept any liability whatsoever in respect of any products purchased through unauthorized sales channel.

- JOULWATT TECHNOLOGY CO.,LTD PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, SAFETY INFORMATION AND OTHER RESOURCES, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

Copyright © 2019 JoulWatt

All rights are reserved by Joulwatt Technology Co.,Ltd